Il y a désormais un nouveau challenger ayant la capacité de produire en masse des puces dont les transistors ne mesurent pas plus de 3 nanomètres : TSMC (Taiwan Semiconductor Manufacturing Company). L’industriel taïwanais doit en effet tenir une petite cérémonie le 29 décembre pour marquer le coup, selon des sources consultées par DigiTimes le 26.

L’ère des puces 3 nanomètres arrive

Les puces 3 nanomètres (nm) constituent le nouvel horizon de l’industrie high-tech à court et moyen terme. Aujourd’hui, il n’y a presque pas d’entreprises dans le monde qui peuvent fabriquer des composants dotés d’une telle finesse de gravure à une échelle industrielle. Samsung a été le premier à se lancer cet été. Maintenant, c’est au tour de TSMC de franchir le pas.

Il est difficile de saisir l’échelle dans laquelle évoluent d’aussi petits transistors. Un nanomètre équivaut à un milliardième de mètre. C’est infime. Dérisoire. En comparaison, un cheveu est 50 000 fois plus épais. Il serait immense à côté du transistor de TSMC. Mais il est d’une taille proche des transistors qui équipent les puces les plus avancées, en 5 et 7 nm.

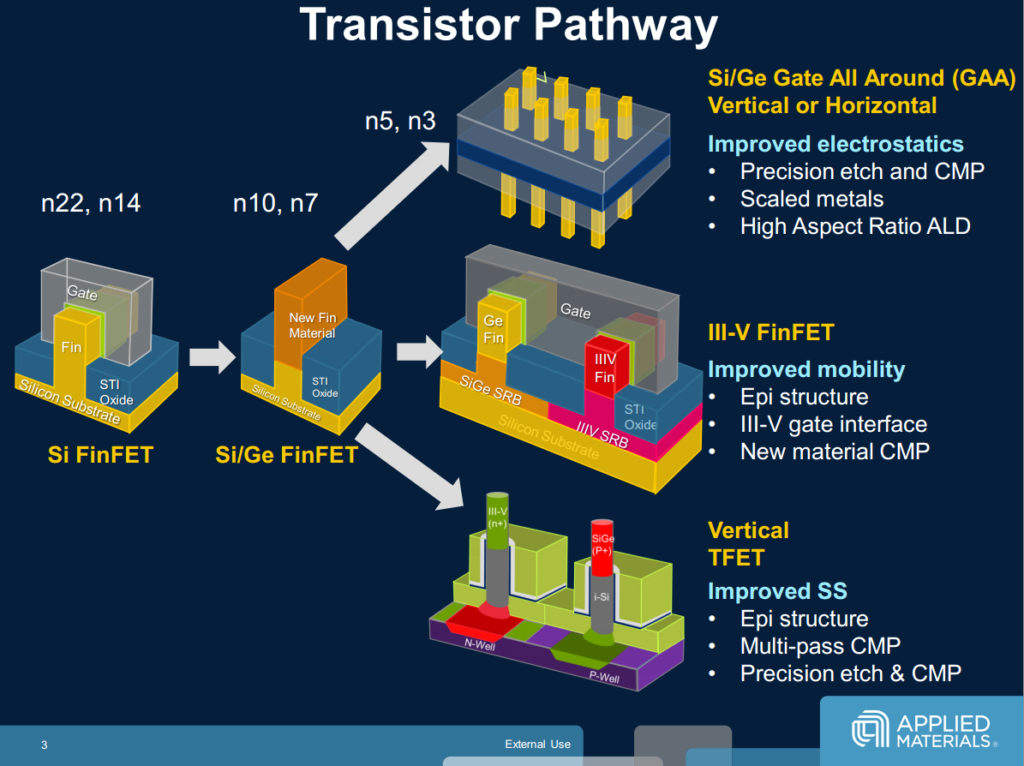

Dans les faits, l’évolution des transistors se fait au niveau de leur géométrie, plus sur leur taille, qu’il devient de plus en plus difficile à abaisser. Ainsi, les industriels ont commencé à délaisser une approche « plate » pour une logique en « trois dimensions ». Ces modifications dans la structure ont pu être observées à partir de 2010 et les puces en 22 puis 14 nm.

Un premier palier a été atteint avec la technologie dite FinFET (fin field-effect transistor, soit transistor à effet de champ à ailettes). Ce procédé a été employé pour les transistors de 22, 14, 10 et 7 nm. Est arrivée ensuite la méthode « GAAFET » (gate-all-around) pour passer le cap des 7 et 5 nm. Le GAAFET entoure le transistor d’une sorte de portail.

Aujourd’hui, TSMC produit déjà des puces en 5 nm pour le compte d’Apple, à travers la puce Apple A16 Bionic. Celle-ci se trouve dans les smartphones les plus pointus de la marque américaine, à savoir l’iPhone 14 Pro et l’iPhone 14 Pro Max. On peut penser que la nouvelle génération de transistors en 3 nm équipera en 2023 les futurs produits de la firme de Cupertino.

+ rapide, + pratique, + exclusif

Zéro publicité, fonctions avancées de lecture, articles résumés par l'I.A, contenus exclusifs et plus encore.

Découvrez les nombreux avantages de Numerama+.

Vous avez lu 0 articles sur Numerama ce mois-ci

Tout le monde n'a pas les moyens de payer pour l'information.

C'est pourquoi nous maintenons notre journalisme ouvert à tous.

Mais si vous le pouvez,

voici trois bonnes raisons de soutenir notre travail :

- 1 Numerama+ contribue à offrir une expérience gratuite à tous les lecteurs de Numerama.

- 2 Vous profiterez d'une lecture sans publicité, de nombreuses fonctions avancées de lecture et des contenus exclusifs.

- 3 Aider Numerama dans sa mission : comprendre le présent pour anticiper l'avenir.

Si vous croyez en un web gratuit et à une information de qualité accessible au plus grand nombre, rejoignez Numerama+.

Toute l'actu tech en un clin d'œil

Ajoutez Numerama à votre écran d'accueil et restez connectés au futur !

Marre des réseaux sociaux ? Rejoignez la communauté Numerama sur WhatsApp !